Vikram Adve María Jesús Garzarán Paul Petersen (Eds.)

# Languages and Compilers for Parallel Computing

20th International Workshop, LCPC 2007 Urbana, IL, USA, October 2007 Revised Selected Papers

#### Lecture Notes in Computer Science

5234

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Vikram Adve María Jesús Garzarán Paul Petersen (Eds.)

### Languages and Compilers for Parallel Computing

20th International Workshop, LCPC 2007 Urbana, IL, USA, October 11-13, 2007 Revised Selected Papers

#### Volume Editors

Vikram Adve

María Jesús Garzarán

University of Illinois at Urbana-Champaign

Department of Computer Science

Thomas M. Siebel Center for Computer Science

201 N. Goodwin Ave, Urbana, IL, 61801, USA

E-mail: {vadve,garzaran}@cs.uiuc.edu

Paul Petersen Intel Corporation 1906 Fox Drive, Champaign, IL, 61820, USA E-mail: paul.petersen@intel.com

Library of Congress Control Number: 2008932585

CR Subject Classification (1998): D.1.3, C.2.4, D.4.2, H.3.4, D.2

LNCS Sublibrary: SL 1 – Theoretical Computer Science and General Issues

ISSN 0302-9743

ISBN-10 3-540-85260-3 Springer Berlin Heidelberg New York ISBN-13 978-3-540-85260-5 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2008 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12455096 06/3180 5 4 3 2 1 0

#### **Preface**

It is our pleasure to present the papers from the 20th International Workshop on Languages and Compilers for Parallel Computing! For the past 19 years, this workshop has been one of the primary venues for presenting and learning about a wide range of current research in parallel computing. We believe that tradition has continued in this, the 20th year of the workshop.

This year, we received 49 paper submissions from 10 countries. About a quarter of the papers (12 out of 49) included authors from industry. We selected 23 papers to be presented at the workshop, for an acceptance rate of 47%, which was similar to that of the last two years. Each paper received at least three reviews, with about two-thirds of the papers getting four or more reviews each. Most papers also received at least one review from an external reviewer. The committee held a full-day teleconference to discuss the reviews and select papers. Program Committee members who had a conflict with a paper left the call when that paper was being discussed. There were seven submissions that included Program Committee members as co-authors. These papers were evaluated more stringently and four of seven were accepted.

The workshop this year also included two exciting special events. First, David Kirk, Chief Scientist of nVidia and a member of the National Academy of Engineering, gave a keynote talk on using highly multithreaded graphics processors for accelerating general-purpose parallel computing applications. Kirk and nVidia have led the drive to make the high parallelism in graphics processors more easily accessible for a wide range of applications beyond traditional graphics processing, and this talk gave LCPC attendees a valuable perspective on the potential of this work.

Second, a special panel was held on Friday morning to commemorate the 20th year of LCPC. This panel, organized and moderated by Steering Committee Chair David Padua, was scheduled for an entire session to allow seven leaders in parallel computing to give their perspective on how the field has evolved over the past 20 years, and what the major challenges are for the future. The panel included a number of luminaries in parallel computing – Arvind (MIT), David Kuck (Intel), Monica Lam (Stanford University), Alexandru Nicolau (University of California Irvine), Keshav Pingali (University of Texas, Austin), Burton Smith (Microsoft Research), and Michael Wolfe (The Portland Group). Our thanks to David Padua for organizing this panel.

We would like to thank the many people who contributed valuable time and effort to making LCPC 2007 a success. Most importantly, we want to thank all the members of the community who submitted papers to the workshop. This workshop is, in the end, an (incomplete) representation of the results of their hard work. Second, the Program Committee worked hard to review 12–13 papers each and to participate in the all-day Program Committee teleconference. The quality of

#### VI Preface

the technical program owes much to their effort. In his role as Steering Committee Chair, David Padua provided valuable guidance and support. He also lent his stack of 19 previous LCPC proceedings to mark the occasion!

Finally, Sheila Clark put in tremendous effort behind the scenes to manage many organizational details for the workshop and we would not have been able to pull it off without all her help.

October 2007

Vikram Adve María Jesús Garzarán Paul Petersen

#### Organization

LCPC 2007 was organized by the Steering and Program Committees.

#### General/Program Co-chairs

Vikram Adve University of Illinois at Urbana-Champaign María Jesús Garzarán University of Illinois at Urbana-Champaign

Paul Petersen Intel Corporation

#### **Program Committee**

Vikram Adve University of Illinois at Urbana-Champaign

Gheorghe Almási IBM Research

José Nelson Amaral University of Alberta, Canada

Eduard Ayguadé Universitat Politécnica de Catalunya, Spain

Gerald Baumgartner Louisiana State University

Călin Caşcaval IBM Research

María Jesús Garzarán University of Illinois at Urbana-Champaign

Sam Midkiff Purdue University Paul Petersen Intel Corporation

J. Ramanujam Louisiana State University

P. Sadayappan Ohio State University

Peng Wu IBM Research

#### Steering Committee

Rudolf Eigenmann Purdue University

Alex Nicolau UC Irvine

David Padua University of Illinois at Urbana-Champaign

Lawrence Rauchwerger Texas A&M University

#### **Sponsoring Institution**

University of Illinois at Urbana-Champaign Siebel Center for Computer Science Urbana, Illinois, October 11–13, 2007

#### Referees

R. Garg

M.J. Garzarán

P. Petersen V. Adve R. Ghiya G. Agrawal M. Girkar C. Pickett G. Almasi M. Gonzalez K. Pingali J.N. Amaral A. Gotsman J. Ramanujam E. Ayguadé J. Guo A. Ramirez M. Baskaran S. Hack A. Rountev G. Baumgartner J. Hoeflinger R. Rugina A. Kejariwal P. Berube P. Sadayappan R. Bocchino G. Kondrak E. Salami U. Bondhugula D. Koppelman R. Schreiber S. Krishnamoorthy J. Brodman P. Sdayappan C. Caşcaval K. Laufer A. Sidelnik L. Ceze O. Lhotak K. Strauss A. Chakravarti Z. Sura X. Martorell A. Cohen L. Meadows D. Tarditi G. Dozsa J. Mellor-Crummey X. Tian P. Unnikrishnan A. Eichenberger S. Midkiff R. Eigenmann R. Niewiadomski N. Vasilache B. Fraguela R. Wilhelm D. Nikolopoulos F. Franchetti R. Nishtala P. Wu

S. Pande

S. Parthasarathy

Y. Zheng

P. Zhao

#### LCPC at Illinois

## Keynote Presentation: NVIDIA CUDA Software and GPU Parallel Computing Architecture

David Kirk, Chief Scientist, nVidia Corp.

Abstract. In the past, graphics processors were special-purpose hard-wired application accelerators, suitable only for conventional rasterization-style graphics applications. Modern GPUs are now fully programmable, massively parallel floating point processors. This talk describes NVIDIA's massively multithreaded computing architecture and CUDA software for GPU computing. The architecture is a scalable, highly parallel architecture that delivers high throughput for data-intensive processing. Although not truly general-purpose processors, GPUs can now be used for a wide variety of compute-intensive applications beyond graphics.

#### Panel I: How Is Multicore Programming Different from Traditional Parallel Programming?

Panelists:

Arch Robison (Intel)

Călin Cașcaval (IBM Research)

Wen-mei Hwu (University of Illinois at Urbana-Champaign)

Hironori Kasahara (Waseda University, Japan) and

Gudula Rünger (Chemnitz University of Technology, Germany)  ${\it Moderator:}$

Vikram Adve (University of Illinois at Urbana-Champaign)

#### Panel II: What Have We Learned After 20 LCPCs?

Panelists:

David Kuck (Intel)

Arvind (MIT)

Monica Lam (Stanford University)

Alexandru Nicolau (University of California Irvine)

Keshav Pingali (University of Texas, Austin)

Burton Smith (Microsoft Research) and

Michael Wolfe (the Portland Group)

Moderator:

David Padua (University of Illinois at Urbana-Champaign)

#### **Table of Contents**

#### Reliability

| Compiler-Enhanced Incremental Checkpointing                                                                                                                           | 1   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Techniques for Efficient Software Checking                                                                                                                            | 16  |

| Languages                                                                                                                                                             |     |

| Revisiting SIMD Programming                                                                                                                                           | 32  |

| Multidimensional Blocking in UPC                                                                                                                                      | 47  |

| An Experimental Evaluation of the New OpenMP Tasking Model<br><i>Eduard Ayguadé, Alejandro Duran, Jay Hoeflinger,</i><br><i>Federico Massaioli, and Xavier Teruel</i> | 63  |

| Language Extensions in Support of Compiler Parallelization Jun Shirako, Hironori Kasahara, and Vivek Sarkar                                                           | 78  |

| Parallel Compiler Technology I                                                                                                                                        |     |

| Concurrency Analysis for Shared Memory Programs with Textually Unaligned Barriers                                                                                     | 95  |

| Iteration Disambiguation for Parallelism Identification in Time-Sliced Applications                                                                                   | 110 |

| A Novel Asynchronous Software Cache Implementation for the Cell-BE Processor                                                                                          | 125 |

| Pillar: A Parallel Implementation Language                                                                                               | 141 |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Libraries                                                                                                                                |     |

| Associative Parallel Containers in STAPL                                                                                                 | 156 |

| Explicit Dependence Metadata in an Active Visual Effects Library Jay L.T. Cornwall, Paul H.J. Kelly, Phil Parsonage, and Bruno Nicoletti | 172 |

| Run-Time Systems and Performance Analysis                                                                                                |     |

| Supporting Huge Address Spaces in a Virtual Machine for Java on a Cluster                                                                | 187 |

| Modeling Relations between Inputs and Dynamic Behavior for General Programs                                                              | 202 |

| Evaluation of RDMA Opportunities in an Object-Oriented DSM                                                                               | 217 |

| Automatic Communication Performance Debugging in PGAS Languages                                                                          | 232 |

| Parallel Compiler Technology II                                                                                                          |     |

| Exploiting SIMD Parallelism with the CGIS Compiler Framework Nicolas Fritz, Philipp Lucas, and Reinhard Wilhelm                          | 246 |

| Critical Block Scheduling: A Thread-Level Parallelizing Mechanism for a Heterogeneous Chip Multiprocessor Architecture                   | 261 |

| Languages II                                                                                                                             |     |

| Capsules: Expressing Composable Computations in a Parallel Programming Model                                                             | 276 |

| Table of Contents                                                                                                    | XV  |

|----------------------------------------------------------------------------------------------------------------------|-----|

| Communicating Multiprocessor-Tasks                                                                                   | 292 |

| General Compiler Techniques                                                                                          |     |

| An Effective Automated Approach to Specialization of Code                                                            | 308 |

| Flow-Sensitive Loop-Variant Variable Classification in Linear Time Yixin Shou, Robert van Engelen, and Johnnie Birch | 323 |

| Using ZBDDs in Points-to Analysis                                                                                    | 338 |

| Author Index                                                                                                         | 353 |

#### Compiler-Enhanced Incremental Checkpointing

Greg Bronevetsky<sup>1</sup>, Daniel Marques<sup>2</sup>, Keshav Pingali<sup>2</sup>, and Radu Rugina<sup>3</sup>

<sup>1</sup> Center for Applied Scientific Computing, Lawrence Livermore National Laboratory, Livermore, CA 94551, USA greg@bronevetsky.com

<sup>2</sup> Department of Computer Sciences, The University of Texas at Austin, Austin, TX 78712, USA

daniel@ices.utexas.edu, pingali@cs.utexas.edu

<sup>3</sup> Department of Computer Science, Cornell University, Ithaca, NY 14850, USA rugina@cs.cornell.edu

Abstract. As modern supercomputing systems reach the peta-flop performance range, they grow in both size and complexity. This makes them increasingly vulnerable to failures from a variety of causes. Checkpointing is a popular technique for tolerating such failures in that it allows applications to periodically save their state and restart the computation after a failure. Although a variety of automated system-level checkpointing solutions are currently available to HPC users, manual application-level checkpointing remains by far the most popular approach because of its superior performance. This paper focuses on improving the performance of automated checkpointing via a compiler analysis for incremental checkpointing. This analysis is shown to significantly reduce checkpoint sizes (upto 78%) and to enable asynchronous checkpointing.

#### 1 Introduction

The dramatic growth in supercomputing system capability from the tera-flop to the peta-flop range has resulted in a dramatic increase in system complexity. While efforts have been made to limit the complexity of the Operating System used by these machines, their component counts have continued to grow. Even as systems like BlueGene/L [3] and the upcoming RoadRunner grow to more than 100,000 processors and tens of TBs of RAM, future designs promise to exceed these limits by large margins. While large supercomputers are made from high-quality components, increasing components counts make them vulnerable to faults, including hardware breakdowns [11] and soft errors [6].

Checkpointing is a popular technique for tolerating failures. The state of the application is periodically saved to reliable storage and on failure, the application rolls back to a prior state. However, automated checkpointing can be very

expensive due to the amount of data saved and the amount of time that the application loses while being blocked. For example, dumping all of RAM on a 128k-processor BlueGene/L supercomputer to a parallel file system would take approximately 20 minutes [9]. Incremental checkpointing [10] is one technique that can reduce the cost of checkpointing. A runtime monitor keeps track of any application writes. If it detects that a given memory region has not been modified between two adjacent checkpoints, this region is omitted from the second checkpoint, thus reducing the amount of data that needs to be saved. Possible monitors that have been explored in the past include virtual memory fault handlers [5], page table dirty bits and cryptographic encoding techniques [4].

When virtual memory fault handlers are used to track application writes, it is possible to further optimize the checkpointing process via a technique called "copy-on-write checkpointing" or more generally, "asynchronous checkpointing". At each checkpoint all pages that need to be checkpointed are marked non-writable and placed on a write-out queue. The application is then allowed to continue executing, while a separate thread asynchronously saves pages on the write-out queue. When the checkpointing thread is finished saving a given page, the page is marked writable. If the application tries to write to a page that hasn't yet been saved, the segmentation fault handler is called, a copy of the page is placed in the write-out queue and the application is allowed to resume execution. The result is that checkpointing is spaced out over a longer period of time, reducing the pressure on the I/O system, while allowing the application to continue executing.

In contrast to prior work, which uses runtime techniques for monitoring application writes, this paper presents a compile-time analysis for tracking such writes. Given an application that has been manually annotated with calls to a checkpoint function, for each array the analysis identifies points in the code such that either

- there exist no writes to the array between the point in the code and the next checkpoint and/or

- there exist no writes to the array between the last checkpoint and the point in the code

When the analysis detects that a given array is not modified between two checkpoints, this array is omitted from the second checkpoint. Furthermore, the analysis enables asynchronous checkpointing by allowing the checkpointing thread to save a given array during the period of time while there are no writes to it. Because the compiler analysis can identify write-free regions that begin before the checkpoint itself, it allows asynchronous checkpointing to begin earlier than is possible with purely runtime solutions. However, because it works at array granularity rather than the page- or word-granularity of runtime monitoring mechanisms, it can be more conservative in its decisions. Furthermore, the analysis makes the assumption that a checkpoint is taken every time the checkpoint function is called, which makes it more complex for users to target a specific checkpointing frequency.

While prior work has looked at compiler analyses for checkpoint optimization [7] [12], it has focused on pure compiler solutions that reduce the amount of data checkpointed. Our work presents a hybrid compiler/runtime approach that uses the compiler to optimize certain portions of an otherwise runtime checkpointing solution. This allows us to both reduce the amount of data being checkpointed as well as support purely runtime techniques such as asynchronous checkpointing.

#### 2 Compiler/Runtime Interface

Our incremental checkpointing system is divided into run-time and compiletime components. The checkpointing runtime may either checkpoint application memory inside of checkpoint calls or include an extra thread that checkpoints asynchronously. Two checkpointing policies are offered. Memory regions that do not contain arrays (a small portion of the code in most scientific applications) are saved in a blocking fashion during calls to checkpoint. Arrays are dealt with in an incremental and possibly asynchronous fashion, as directed by the annotations placed by the compiler. The compiler annotates the source code with calls to the following functions:

- add\_array(ptr, size) Called when an array comes into scope to identify the array's memory region.

- remove\_array(ptr) Called when an array leaves scope. Memory regions

that have been added but not removed are treated incrementally by the

checkpointing runtime.

- start\_chkpt(ptr) Called to indicate that the array that contains the address ptr will not be written to until the next checkpoint. The runtime may place this array on the write-out queue and begin to asynchronously checkpoint this array.

- end\_chkpt(ptr) Called to indicate that the array that contains the address ptr is about to be written to. The end\_chkpt call must block until the checkpointing thread has finished saving the array. It is guaranteed that there exist no writes to the array between any checkpoint and the call to end\_chkpt.

Overall, the runtime is allowed to asynchronously checkpoint a given array between calls to start\_chkpt and end\_chkpt that refer to this array. If start\_chkpt is not called for a given array between two adjacent checkpoints, this array may be omitted from the second checkpoint because it is known that it was not written to between the checkpoints.

For a more intuitive idea of how this API is used, consider the transformation in Figure 1. The original code contains two checkpoint calls, with assignments to arrays A and B in between. The code within the ...'s does not contain any writes to A or B. It is transformed to include calls to start\_chkpt and end\_chkpt around the writes. Note that while end\_chkpt(B) is placed immediately before the write to B, start\_chkpt(B) must be placed at the end of B's write loop. This

```

Original Code

Transformed Code

checkpoint();

checkpoint();

end_chkpt(A);

A[\ldots] = \ldots;

A[\ldots] = \ldots;

for(...) {

start_chkpt(A);

B[\ldots] = \ldots;

for(...) {

end_chkpt(B);

B[\ldots] = \ldots;

checkpoint();

start_chkpt(B);

checkpoint();

```

Fig. 1. Transformation example

is because a start\_chkpt(B) call inside the loop may be followed by writes to B in subsequent iterations. Placing the call immediately after the loop ensures that this cannot happen.

#### 3 Compiler Analysis

The incremental checkpointing analysis is a dataflow analysis that consists of forward and backward components. The forward component, called the *Dirty Analysis*, identifies the first write to each array after a checkpoint. The backward, called the *Will-Write* analysis, identifies the last write to each array before a checkpoint.

#### 3.1 Basic Analysis

For each array at each node n in a function's control-flow graph(CFG) the analysis maintains two bits of information:

- mustDirty[n](array): True if there must exist a write to array along every path from a checkpoint call to this point in the code; False otherwise. Corresponds to the dataflow information immediately  $before \ n$ .

- mayWillWrite[n](array): True if there may exist a write to array along some path from a this point in the code to a checkpoint call; False otherwise.

Corresponds to the dataflow information immediately after n.

This information is propagated through the CFG using the dataflow formulas in Figure 2. The Dirty and Will-Write analyses start at the top and bottom of each function's CFG, respectively, in a state where all arrays are considered to

be clean (e.g. consistent with the previous, next checkpoint, respectively). They then propagate forward and backward, respectively, through the CFG, setting each array's write bit to True when it encounters a write to this array. When each analysis reaches a checkpoint call, it resets the state of all the arrays to False. For the Dirty Analysis this is because all dirty arrays will become clean because they are checkpointed. For the WillWrite Analysis this is because at the point immediately before a checkpoint there exist no writes to any arrays until the next checkpoint, which is the checkpoint in question.

$$mustDirty[n](array) = \begin{cases} False & \text{if } n = \text{first node} \\ \bigcap_{m \in pred(n)} mustDirtyAfter[m](array) & \text{otherwise} \end{cases}$$

$$mustDirtyAfter[m](array) = \llbracket m \rrbracket (mustDirty[m](array), array)$$

$$mayWillWrite[n](array) = \begin{cases} False & \text{if } n = \text{last node} \\ \bigcup_{m \in succ(n)} mayWillWriteBefore[m](array) & \text{otherwise} \end{cases}$$

$$mayWillWriteBefore[m](array) = \llbracket m \rrbracket (mayWillWrite[m](array), array)$$

$$\begin{cases} Statement \ m \\ array[expr] = expr \end{cases} \frac{\llbracket m \rrbracket (val, array)}{True}$$

checkpoint()

|                 | Other           | · ·       | ui     |               |

|-----------------|-----------------|-----------|--------|---------------|

|                 |                 |           |        |               |

|                 |                 |           |        |               |

| Fig. 2. Dataflo | ow formulas for | Dirty and | Will-W | rite analyses |

The application source code is annotated with calls to start\_chkpt and end\_chkpt using the algorithm in Figure 3. Such calls are added in three situations. First, end\_chkpt (array) is inserted immediately before node n if n is a write to array and it is not preceded by any other write to array along some path that starts at a call to checkpoint and ends with node n. Second, start\_chkpt(array) is inserted immediately after node n if n is a write to array and there do not exist any more writes to array along any path that starts with n and ends at a checkpoint call. Third, a start\_chkpt(array) is inserted on a CFG branching edge  $m \to n$  if mayWillWrite[n](array) is true at m, but false at n, due to merging of dataflow information at branching point m. This treatment is especially important when an array is being written inside a loop. In this case, mayWillWrite[n](array) is true at all points in the loop body, since the array may be written in subsequent loop iterations. The flag becomes false on the edge that branches out of the loop, and the compiler inserts the start\_chkpt(array) call on this edge.

Because the Dirty analysis is based on *must-write* information, end\_chkpt calls are conservatively placed as late as possible after a checkpoint. Furthermore, the Will-Write analysis' use of *may-write* information conservatively places start\_save calls as early as possible before a checkpoint.

To provide an intuition of how the analysis works, consider the example in Figure 4. In particular, consider the points in the code where must Dirty

```

foreach (array array), foreach (CFG node n) in application

// if node n is the first write to array since the last checkpoint call

if (mustDirty[n](array) = False \land mustDirtyAfter[n](array) = True)

place end_chkpt(array) immediately before n

// if node n is the last write to array until the next checkpoint call

if (mayWillWriteBefore[n](array) = True \land mayWillWrite[n](array) = False)

place start_chkpt(array) immediately after n

// if node n follows the last write on a branch where array is no longer written

if (mayWillWriteBefore[n](array) = False \land

\exists m \in pred(n). mayWillWrite[m](array) = True)

place start_chkpt(array) on edge m \rightarrow n

```

Fig. 3. Transformation for inserting calls to start\_chkpt and end\_chkpt

and mayWillWrite change from False to True. These are the points where end\_chkpt and start\_chkpt calls are inserted.

#### 3.2 Loop-Sensitive Analysis

While the basic analysis performs correct transformations, it has performance problems when it is applied to loops. This can be seen in the transformed code in Figure 4. While start\_chkpt(B) is placed immediately after the loop that writes to B, end\_chkpt(B) is placed inside the loop, immediately before the write to B itself. This happens because the placement of end\_chkpt depends on must-write information, instead of the may-write information used in placing start\_chkpt. While this placement is conservative, it becomes problematic in the case where the first post-checkpoint write to an array happens in a small, deeply-nested loop, which are very common in scientific computing. In this case end\_chkpt will be called during each iteration of the loop, causing a potentially severe overhead.

| Original Code            | Code with Dirty States                             | Code with Will-Write States                        | Transformed Code         |

|--------------------------|----------------------------------------------------|----------------------------------------------------|--------------------------|

| <pre>checkpoint();</pre> | checkpoint(); $[A \rightarrow F, B \rightarrow F]$ | checkpoint(); $[A \rightarrow T, B \rightarrow T]$ | <pre>checkpoint();</pre> |

|                          | $\dots$ [A $\rightarrow$ F,B $\rightarrow$ F]      | [A $ ightarrow$ T,B $ ightarrow$ T]                |                          |

| A[;                      | $A[]=; [A \rightarrow F, B \rightarrow F]$         | $A[]=; [A \rightarrow F, B \rightarrow T]$         | <pre>end_chkpt(A);</pre> |

|                          | $\dots$ [A $\rightarrow$ T,B $\rightarrow$ F]      | $[A \rightarrow F, B \rightarrow T]$               | A[;                      |

| for() {                  | for() $\{ [A \rightarrow T, B \rightarrow F] \}$   | for() $\{ [A \rightarrow F, B \rightarrow T] \}$   | start_chkpt(A);          |

|                          | $\dots$ [A $\rightarrow$ T,B $\rightarrow$ F]      | $\dots$ [A $\rightarrow$ F,B $\rightarrow$ T]      |                          |

| B[]=;                    | $B[]=; [A \rightarrow T, B \rightarrow F]$         | $B[]=; [A \rightarrow F, B \rightarrow T]$         | for() {                  |

|                          | $\dots$ [A $\rightarrow$ T,B $\rightarrow$ T]      | $\dots$ [A $\rightarrow$ F,B $\rightarrow$ T]      |                          |

| }                        | $  \} [A \rightarrow T, B \rightarrow T]$          | $\}$ [A $\rightarrow$ F,B $\rightarrow$ T]         | <pre>end_chkpt(B);</pre> |

|                          | $\dots$ [A $\rightarrow$ T,B $\rightarrow$ F]      | $\dots$ [A $\rightarrow$ F,B $\rightarrow$ F]      | B[;                      |

| <pre>checkpoint();</pre> | checkpoint(); $[A \rightarrow T, B \rightarrow F]$ | checkpoint(); $[A \rightarrow F, B \rightarrow F]$ |                          |

|                          |                                                    |                                                    | }                        |

|                          |                                                    |                                                    | start_chkpt(B);          |

|                          |                                                    |                                                    |                          |

|                          |                                                    |                                                    | <pre>checkpoint();</pre> |

Fig. 4. Analysis example

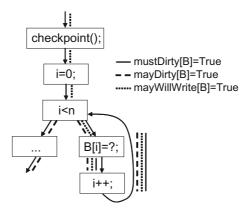

Fig. 5. Dataflow pattern for writes inside loops

To address this problem the above analysis was augmented with a loopdetection heuristic, shown in Figure 5. This heuristic uses may-Dirty information, in addition to the must-Dirty and may-WillWrite information of Section 3 and identifies the patterns of dataflow facts that must hold at the top of the first loop that writes to an array after a checkpoint. Figure 5 contains the CFG of such a loop and identifies the edges in the CFG where the various dataflow facts are True. It can be seen that the pattern at node i < n is:

```

- mustDirty[i < n](B) = False

- mayDirty[i < n](B) = True

- mayWillWrite[i < n](B) = True

```

- pred(i < n) > 1

Furthermore, the CFG edge that points to i < n from outside the loop is the one coming from the predecessor p where mustDirtyAfter[p](B) = False. Thus, by placing end\_chkpt(B) on this incoming edge we can ensure both that end\_chkpt(B) is called before any write to B and that it is not executed in every iteration of the loop.

Since this heuristic only applies to loops, it does not place end\_chkpt(A) before the write to A in Figure 1. As such, we need to use both rules to ensure that end\_chkpt is placed conservatively. However, if both rules are used then the example in Figure 1 will get two end\_chkpt(B) calls: one before B's write loop and one before the write itself, negating the purpose of the loopsensitive placement strategy. To prevent this from happening we propose an extra EndChkpt-Placed analysis that prevents end\_chkpt(array) from being placed at a given node if there already exists an end\_chkpt(array) on every path from any checkpoint call to the node. EndChkpt-Placed is a forward analysis that is executed as a separate pass from the Dirty and Will-Write passes. It maintains a bit of information for every array at every CFG node. mustEndChkptPlaced[n](array) is set to True if end\_chkpt(array) is to be placed immediately before node n. It is set to False if  $start\_chkpt(array)$  is to be inserted at n. The later rule ensures that the "exclusion-zone" of a given insertion of end\\_chkpt(array) doesn't last past the next checkpoint call.

To implement this rule the loop-sensitive analysis maintains for each CFG node n the following additional dataflow information:

- mayDirty[n](array): True if there may exist a write to array along some path from a **checkpoint** call to this point in the code; False otherwise. Corresponds to the dataflow information immediately before n.

- mustEndChkptPlaced[n](array): true if all paths from any checkpoint call

to this point in the code contain a point where a end\_chkpt(array) call will

be placed.

This information is computed as shown in Figure 6. The modified rules for placing end\_chkpt calls are shown in Figure 7 and Figure 8 extends the example in Figure 1 with the new mustEndChkptPlaced information and the new placement of end\_chkpt calls.

#### 3.3 Inter-procedural Analysis

We have extended the above analysis with a context-insensitive, flow-sensitive inter-procedural analysis. The inter-procedural analysis works by applying the data-flow analysis from Section 3.2 to the CFG that contains all of the application's functions. When the analysis reaches a function call node for the first time, it computes a summary for this function. This is done by applying the dataflow analysis using the formulas in Figure 6 but with a modified lattice.

In addition to the standard True and False, we introduce an additional Unsetstate that appears below True and False in the lattice. All the dataflow facts for all arrays are initialized to *Unset* at the start or end of the function (start for the forward analyses and end for the backward analysis). The standard analysis is then executed on the function using the extended lattice, with *Unset* being treated as False for the purposes of the EndChkpt-Placed analysis. If the state of a given array remains *Unset* at the end of a given pass, this means that it was not modified by the pass. In the case of the Dirty and Will-Write analyses this means that the array is not written to inside the function. In the case of the EndChkpt-Placed analysis, this means that no end\_chkpt calls are placed for this array inside the function. The function summary then is the dataflow facts for each array at the opposite end of the function: end for the forward analyses and start for the backward analysis. Function calls are processed by applying the function summary as a mask on all dataflow state. If dataFlow[array] = Unset in the function summary, array's mapping is not changed in the caller. However, if dataFlow[array] = True or False in the summary, the corresponding dataflow fact for array is changed to True or False in the caller.

```

mayDirty[n](array) = \begin{cases} False & \text{if } n = \text{first} \\ \bigcup_{m \in pred(n)} mayDirtyAfter[m](array) & \text{otherwise} \end{cases}

if n = first node

mayDirtyAfter[m](array) = [m](mayDirty[m](array), array)

mustEndChkptPlaced[n](array) =

\begin{cases} False \\ \bigcap_{m \in vred(n)} mustEndChkptPlacedAfter[m](array) \end{cases}

if n = first node

otherwise

mustEndChkptPlacedAfter[m](array) =

if \neg placeStartChkptNode(m, array) \land

\neg \exists l \in pred(m). placeStartChkptEdge(l, m, array)) then

else if (placeEndChkptNode(m, array) \lor

\exists l \in pred(m). \ placeEndChkptEdge(l, m, array)) \ then

else mustEndChkptPlaced[m](array)

// end_chkpt(array) will be placed immediately before node n if

placeEndChkptNode(n, array) =

// node n is the first write to array since the last checkpoint

(mustDirty[n](array) = False \land mustDirtyAfter[n](array) = True)

// end_chkpt(array) will be placed along the edge m \to n if

placeEndChkptEdge(m, n, array) =

// node n is itself clean but predecessor m is dirty, n contains or is followed

// by a write and predecessor m is not itself preceded by end\_chkpt(array)

(mustDirty[n](array) = False \land mayDirty[n](array) = True \land

mayWillWrite[n](B) = True \land mustDirtyAfter[m](array) = False \land

mustEndChkptPlaced[m](array) = False)

// start_chkpt(array) will be placed immediately after node n if

placeStartChkptNode(n, array) =

// node n is the last write to array until the next checkpoint

(mayWillWriteBefore[n](array) = True \land mayWillWrite[n](array) = False)

// start_chkpt(array) will be placed along the edge m \to n if

placeStartChkptEdge(m, n, array) =

// node n follows the last write to array until the next checkpoint

(mayWillWriteBefore[n](array) = False \land mayWillWrite[m](array) = True)

```

Fig. 6. Dataflow formulas for the loop-sensitive extension

```

foreach (array), foreach (CFG node n) in application if placeEndChkptNode(n, array) place end_chkpt(array) immediately before n if \exists m \in pred(n). placeEndChkptEdge(m, n, array) place end_chkpt(array) on edge m \to n

```

Fig. 7. Loop-sensitive transformation for inserting calls to end\_chkpt

| Original Code            | Code with Must-EndChkptPlaced States                                                                 | Transformed Code           |

|--------------------------|------------------------------------------------------------------------------------------------------|----------------------------|

| <pre>checkpoint();</pre> | $\texttt{checkpoint();}  [\texttt{A} {\rightarrow} \texttt{F}, \texttt{B} {\rightarrow} \texttt{F}]$ | <pre>checkpoint();</pre>   |

|                          | $\dots$ [A $\rightarrow$ F,B $\rightarrow$ F]                                                        |                            |

| A[]=;                    | $A[]=; [A \rightarrow F, B \rightarrow F]$                                                           | <pre>end_chkpt(A);</pre>   |

|                          | $[A \rightarrow T, B \rightarrow F]$                                                                 | A[;                        |

| for() {                  | for() $\{ [A \rightarrow T, B \rightarrow T] \}$                                                     | <pre>start_chkpt(A);</pre> |

|                          | $\dots$ [A $\rightarrow$ T,B $\rightarrow$ T]                                                        |                            |

| B[]=;                    | $B[\ldots] = \ldots; [A \rightarrow T, B \rightarrow T]$                                             | <pre>end_chkpt(B);</pre>   |

|                          | $\dots$ [A $\rightarrow$ T,B $\rightarrow$ T]                                                        | for() {                    |

| }                        | [A $\rightarrow$ T,B $\rightarrow$ T]                                                                |                            |

|                          | $\dots$ [A $\rightarrow$ T,B $\rightarrow$ T]                                                        | B[;                        |

| <pre>checkpoint();</pre> | $\texttt{checkpoint();}  \texttt{[A}{\longrightarrow}\texttt{T,B}{\longrightarrow}\texttt{T]}$       |                            |

|                          |                                                                                                      | }                          |

|                          |                                                                                                      | <pre>start_chkpt(B);</pre> |

|                          |                                                                                                      |                            |

|                          |                                                                                                      | <pre>checkpoint();</pre>   |

Fig. 8. Transformation example with loop-sensitive optimizations

#### 4 Experimental Evaluation

#### 4.1 Experimental Setup

We have evaluated the effectiveness of the above compiler analysis by implementing it on top of the ROSE [8] source-to-source compiler framework and applying it to the OpenMP versions [1] of the NAS Parallel Benchmarks [2]. We have used these codes in sequential mode and have focused on the codes BT, CG, EP, FT, LU, SP. We have omitted MG from our analysis since it uses dynamic multi-dimensional arrays (arrays of pointers to lower-dimensional arrays), which requires additional complex pointer analyses to identify arrays in the code. In contrast, the other codes use simple contiguous arrays, which require no additional reasoning power. Each NAS code was augmented with a checkpoint call at the top of its main compute loop and one immediately after the loop.

The target applications were executed on problem classes S, W and A (S is the smallest of the three and A the largest), on 4-way 2.4Ghz dual-core Opteron SMPs, with 16GB of RAM per node (Atlas cluster at the Lawrence Livermore National Laboratory). Each run was performed on a dedicated node and all reported results are averages of 10 runs. Each application was set to checkpoint

5 times, with the checkpoints spaced evenly throughout the application's execution. This number was chosen to allow us to sample the different checkpoint sizes that may exist in different parts of the application without forcing the application to take a checkpoint during every single iteration, which would have been unrealistically frequent.

The transformed codes were evaluated with a model checkpointing runtime that implements the API from Section 2 and simulates the costs of a real checkpointer. It performs the same state tracking as a real checkpointer but instead of actually saving application state, it simply sleeps for an appropriate period of time. One side-effect of this is the fact that our checkpointer does not simulate the overheads due to saving variables other than arrays. However, since in the NAS benchmarks such variables make up a tiny fraction of overall state, the resulting measurement error is small. Furthermore, since the model checkpointer can sleep for any amount of time, it can simulate checkpointing performance for a wide variety of storage I/O bandwidths.

The model checkpointer can be run in both a blocking and a non-blocking mode. In blocking mode the checkpointer does not spawn an asynchronous checkpointing thread but instead saves all live state inside the main thread's checkpoint calls. The model runtime can simulate both a basic checkpointer, which saves all state and an incremental checkpointer, which only saves the state that has changed since the last checkpoint. In particular, in incremental mode the model checkpointer simulates the checkpointing of any array for which start\_chkpt has been called since the last checkpoint call. Arrays for which start\_chkpt has not been called are ignored.

In non-blocking mode, the model checkpointer spawns off an asynchronous checkpointing thread. The thread maintains a write-out queue of memory regions to save and continuously pulls memory regions the queue, sleeping for as long at it takes to save the next memory region to disk at the given I/O bandwidth. When the main thread calls <code>end\_chkpt</code> for one array, it may be that the checkpointing thread is currently sleeping on another array. To control the amount of waiting time, the model checkpointer breaks arrays up into smaller blocks and simulates checkpointing at block granularity. <code>start\_chkpt(array)</code> inserts <code>array</code>'s blocks at the end of the write-out queue. We also tried spreading the new array's blocks evenly across the queue but did not find a substantial or consistent performance difference between the two policies.

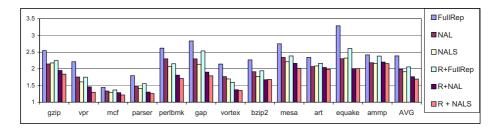

#### 4.2 Incremental Checkpointing

We evaluated the effectiveness of the above analysis for incremental checkpointing by comparing the performance of two configurations of the model checkpointer's blocking mode:

- CHKPT\_ALL simulates the checkpointing of all application arrays inside each checkpoint call.

- CHKPT\_INCR same as CHKPT\_ALL but omits any arrays for which start\_chkpt hasn't been called since the last checkpoint call.

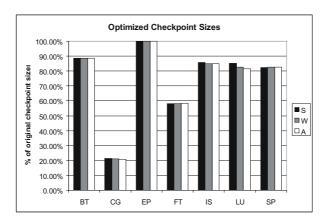

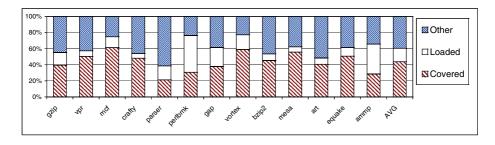

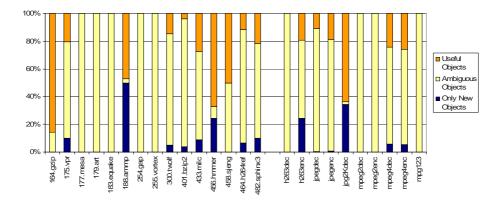

Fig. 9. Checkpoint sizes in CHKPT\_INCR as a fraction of checkpoint sizes in CHKPT\_ALL

We first compare the checkpoint sizes generated by the two modes. In the context of the NAS codes, which have a initialization phase, followed by a main compute loop, the primary effect of the above analysis is to eliminate write-once arrays from checkpointing. These are the arrays that are written to during the initialization phase and then only read from during the main compute loop. As such, since there do not exist any start\_chkpt calls for these arrays during the main compute loop, they are only saved during the first checkpoint and omitted in subsequent checkpoints.

The measured reductions in checkpoint size are shown in Figure 9. It can be seen that even using array granularity, incremental checkpointing can result in a dramatic reduction in checkpoint sizes. Indeed, in CG checkpoints drop to below 22% of their original size, while FT's drop to 60%. Other codes see drops from 0% to 18%. While there are small differences in the effect of incremental checkpointing across different problem sizes, the effect is generally small.

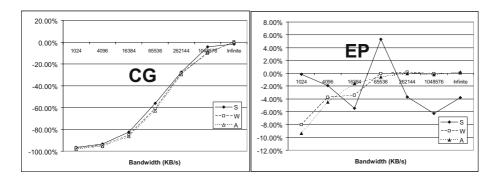

Figure 10 shows the the execution time of an application that uses incremental checkpointing as a percentage of the execution time of one that does not. We show only CG and EP, since the behavior of these codes is similar to that of other codes that have a large or a small checkpoint size reduction, respectively. The x-axis is the I/O bandwidth used in the experiments, ranging from 1 MB/s to 1 GB/s in multiples of 4 and including Infinite bandwidth. This range includes a variety of use-cases, including hard-drives (60MB/s write bandwidth) and 10 Gigabit Ethernet(1GB/s bandwidth). In the case of EP, although there is some difference in performance between the two versions, the effect is at noise level at all bandwidths, with no correlation between execution time and performance. However, for CG, the effect is quite dramatic, ranging from pronounced difference in execution times for low bandwidths, when the cost of checkpointing is important, to a much smaller difference for high bandwidths.

Fig. 10. Relative execution time differences between CHKPT\_INCR and CHKPT\_ALL

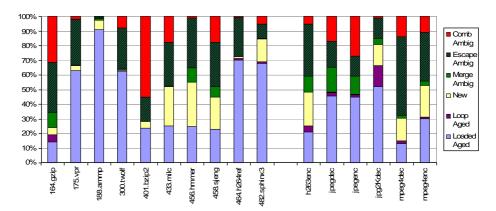

#### 4.3 Asynchronous Checkpointing

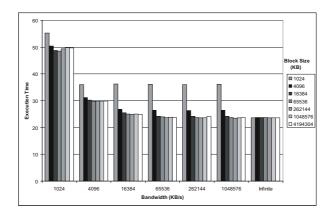

We examined the performance characteristics of asynchronous checkpointing by looking at the relationship between the I/O bandwidth and the block size used for queue management. To this end we examined a range of block sizes ranging from 1KB to 64MB in multiples of 4, using the above bandwidth range. For almost all code/input class/bandwidth combinations we found that the execution times formed a bowl shape, an example of which is shown in Figure 11. This Figure shows LU running on input size W. For each I/O bandwidth we can see high execution times for the largest and the smallest batch size, with faster runs for intermediate batch sizes. Large batch sizes have high overhead because of the increased probability that an end\_chkpt call for some array will occur in the middle of a long wait for a large block of another array. Small batch sizes are a problem because of the increased overhead associated with synchronizing on and manipulating a large number of memory regions. While this work does not address the problem of picking an optimal batch size for a given code/input class/bandwidth combination, we did find that in general the bottom of the bowl stays flat, with a wide variety of batch sizes offering similarly good performance. This suggests that near-optimal batch sizes can be found for a wide variety of combinations. In our experiments, 64KB batches provided near-optimal performance in all configurations examined.

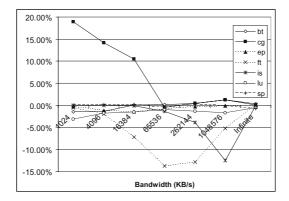

We evaluated the performance of asynchronous checkpointing by picking the best batch size for each code/input size/bandwidth combination and compared its performance to that of blocking incremental checkpointing (the CHKPT\_INCR configuration from above). The result, for input size W, is shown in Figure 4.3. For each application it plots:

$\frac{(\text{execution time w/ asynchronous checkpointing}) - (\text{execution time w/ blocking checkpointing})}{(\text{execution time w/ blocking checkpointing})}$

It can be seen that different applications respond very differently to the two algorithms. Whereas CG performs better with asynchronous checkpointing, FT and IS

Fig. 11. Execution times for different bandwidths and batch sizes (LU-W)

Fig. 12. Relative execution times for asynchronous vs blocking checkpointing (Class W)

tend to perform better with blocking checkpointing. Input class  ${\tt A}$  shows very similar results, while class  ${\tt S}$  exhibits a stronger preference for blocking checkpointing.

While intuitively it may appear that asynchronous checkpointing should always perform better than blocking checkpointing, these experiments show that there are some interference effects that complicate this simple analysis. While the full reason for this effect is still under investigation, it appears that the additional synchronization required to implement asynchronous checkpointing may have a negative performance impact. In particular, each call by the application thread to start\_chkpt and end\_chkpt requires synchronization with the asynchronous checkpointing thread.

#### 5 Summary

We have presented a novel compiler analysis for optimizing automated checkpointing. Given an application that has been augmented by the user with calls to a checkpoint function, the analysis identifies regions in the code that do not have any writes to a given array. This information can be used to reduce the amount of data checkpointed and to asynchronously checkpoint this data in a separate thread. In our experiments with the NAS Parallel Benchmarks we have found that this analysis reduces checkpoint sizes by between 15% and 78% for most of the codes. These checkpoint size reductions were found to have a notable effect on checkpointing performance. Furthermore, we evaluated the performance of compiler-enabled asynchronous checkpointing. Although our experiments showed that asynchronous checkpointing can sometimes be better than blocking checkpointing, we discovered that this is frequently not the case. As such, the choice between asynchronous and blocking checkpointing depends on the application itself.

#### References

- 1. http://phase.hpcc.jp/Omni/benchmarks/NPB

- 2. http://www.nas.nasa.gov/Software/NPB

- 3. Adiga, N.R., Almasi, G., Almasi, G.S., Aridor, Y., Barik, R., Beece, D., Bellofatto, R., Bhanot, G., Bickford, R., Blumrich, M., Bright, A.A., Brunleroto J.: An overview of the bluegene/l supercomputer. In: IEEE/ACM Supercomputing Conference (2002)

- Agarwal, S., Garg, R., Gupta, M.S., Moreira, J.: Adaptive incremental checkpointing for massively parallel systems. In: Proceedings of the 18th International Conference on Supercomputing (ICS), pp. 277–286 (2004)

- Gioiosa, R., Sancho, J.C., Jiang, S., Petrini, F.: Transparent, incremental checkpointing at kernel level: a foundation for fault tolerance for parallel computers. In: Supercomputing (November 2005)

- Michalak, S.E., Harris, K.W., Hengartner, N.W., Takala, B.E., Wender, S.A.: Predicting the number of fatal soft errors in los alamos national laboratorys asc q supercomputer. IEEE Transactions on Device and Materials Reliability 5(3), 329–335 (2005)

- Plank, J.S., Beck, M., Kingsley, G.: Compiler-assisted memory exclusion for fast checkpointing. IEEE Technical Committee on Operating Systems and Application Environments 7(4), 10–14 (Winter 1995)

- 8. Quinlan, D.: Rose: Compiler support for object-oriented frameworks. Parallel Processing Letters 10(2-3), 215–226 (2000)

- 9. Ross, K.C.R., Moreirra, J., Preiffer, W.: Parallel i/o on the ibm blue gene /l system. Technical report, BlueGene Consortium (2005)

- Sancho, J.C., Petrini, F., Johnson, G., Fernandez, J., Frachtenberg, E.: On the feasibility of incremental checkpointing for scientific computing. In: 18th International Parallel and Distributed Processing Symposium (IPDPS), p. 58 (2004)

- Schroeder, B., Gibson, G.A.: A large-scale study of failures in high-performance computing systems. In: Proceedings of the International Conference on Dependable Systems and Networks (DSN) (June 2006)

- Zhang, K., Pande, S.: Efficient application migration under compiler guidance. In: Proceedings of the Conference on Languages, Compilers, and Tools for Embedded Systems, pp. 10–20 (2005)

#### Techniques for Efficient Software Checking\*

Jing Yu, María Jesús Garzarán, and Marc Snir

University of Illinois at Urbana-Champaign {jingyu,garzaran,snir}@cs.uiuc.edu

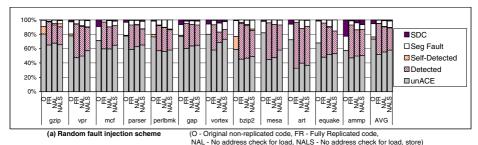

Abstract. Dramatic increases in the number of transistors that can be integrated on a chip make processors more susceptible to radiation-induced transient errors. For commodity chips which are cost- and energy-constrained, we need a flexible and inexpensive technology for fault detection. Software approaches can play a major role for this sector of the market because they need little hardware modifications and can be tailored to fit different requirements of reliability and performance. However, software approaches add a significant overhead.

In this paper we propose two novel techniques that reduce the overhead of software error checking approaches. The first technique uses boolean logic to identify code patterns that correspond to outcome tolerant branches. We develop a compiler algorithm that finds those patterns and removes the unnecessary replicas. In the second technique we evaluate the performance benefit obtained by removing address checks before load and stores. In addition, we evaluate the overheads that can be removed when the register file is protected in hardware.

Our experimental results show that the first technique improves performance by an average 7% for three of the SPEC benchmarks. The second technique can reduce overhead by up-to 50% when the most aggressive optimization is applied.

#### 1 Introduction

Dramatic increases in the number of transistors that can be integrated on a chip will deliver great performance gains. However, it will also expose a major roadblock, namely the poor reliability of the hardware. Indeed, in the near-future environment of low power, low voltage, relatively high frequency, and very small feature size, processors will be more susceptible to transient errors. Transient faults, also known as soft errors are due to impacts from high-energy particles that change the logic values of latches or logic structures [1,2,3,4].

In this new environment, we believe that a Software Checking System has a fundamental role in providing fault detection and recovery. It is possible that high-end architectures will include several hardware-intensive fault-tolerant techniques that are currently supported by IBM mainframes [5], HP NonStop [6] or mission-critical computers [7]. However, commodity multicore chips will likely be

$<sup>^\</sup>star$  This material is based upon work supported by the National Science Foundation under the CSR-AES program Award No. 0615273.

V. Adve, M.J. Garzarán, and P. Petersen (Eds.): LCPC 2007, LNCS 5234, pp. 16–31, 2008.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2008

too cost- and energy-constrained to include such hardware. Instead, we believe that they will likely include only relatively simple hardware primitives, such as parity for certain processor buses and structures, error correction codes (ECC) and scrubbing in the memory hierarchy [8] and low-cost support for memory checkpointing and rollback (e.g., ReVive [9] or SafetyNet [10]). Then they will rely on flexible and inexpensive software technology for error protection.

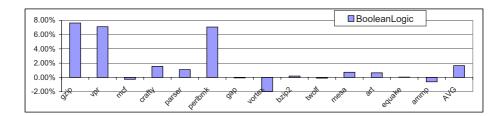

Current software approaches address the problem by replicating the instructions and adding checking instructions to compare the results, but they add a significant overhead. In this paper we propose two novel techniques to reduce the overhead of the software error checking approaches. The first technique is based on the fact that programs already have redundancy, and if the compiler can determine the programs sections where such redundancy exists, it can avoid the replication and later checking. We use boolean logic to identify a code pattern that corresponds to outcome tolerant branches and develop a compiler algorithm that automatically finds those patterns and removes the unnecessary replicas. The second technique is based on the observation that faults that corrupt the application tend to quickly generate other noisy errors such as segmentation faults [11]. Thus, we can reduce replication of the instructions that tend to generate these type of errors, trading reliability for performance. In this paper we remove the checks of the memory addresses and discuss situations where removing these checks affect little to the fault coverage. This occurs when a check of a variable is covered by a later check to the same variable, and thus errors in the first check will be detected by the later checks; and in pointer-chasing, when the data loaded by a load is used immediately by another load. Finally, We also consider the situation where the register file is protected with parity or ECC, such as Intel Itanium [12], Sun UltraSPARC [13] and IBM Power4-6 [14]. We call them register safe platforms.

We have implemented the baseline replication and the proposed techniques using the LLVM Compiler Infrastructure [15] and run experiments on a Pentium 4 using Spec benchmarks. Our results show that the boolean logic technique achieves 7% performance speedup on three benchmarks, and 1.6% on average. If we do not check load addresses, the performance is improved by 20.2%. If we do not check addresses of both load and store, the performance is improved by 24.8%. On platforms where registers are protected in hardware, we can combine these techniques and obtain an average speedup of 35.2% and 40.8%, respectively, and decrease the software checking overhead by 44.9% and 50%, respectively. Our fault injection experiments show that removing address checks before loads only increases Silent Data Corruption (SDC) from 0.27% to 0.35%, and removing address checks for loads and stores raises SDC to 1.11%.

The rest of the paper is organized as follows. Section 2 presents the background and the baseline software checking; Section 3 describes the techniques to detect outcome tolerant branches; Section 4 describes the removal of address checks; Section 5 discusses the benefits of having a register file that is checked in hardware; Section 6 presents our experimental results; Section 7 presents related work, and finally Section 8 concludes the paper.

#### 2 Background and Baseline Software Checking

The use of software approaches for fault tolerance has received significant attention in the research domain. Software techniques such as SWIFT [16] replicate the instructions of the original program and interleave the original instructions and their replicas in the same thread. Memory does not need to be replicated because the memory hierarchy is protected with ECC and scrubbing. Stores, branches, function calls and returns are considered "synchronization" points and checking instructions are inserted before these instructions to validate certain values. Before a store, checking instructions verify that the correct data is stored to the correct memory location. Before a branch, checking instructions verify that the branch takes the appropriate path. Before a function call checking instructions verify the input operands by comparing them against their replica. Before a function return, checking instructions verify the return value by comparing the return register and its replica.

Stores are executed only once, but loads are replicated because the loaded data can be corrupted. However, uncachable loads, such as those from external devices, and loads in a multithreaded program may return different values when executing two consecutive loads to the same memory address; so rather than replicating the load, checking instructions are also added before loads to verify that the address of the load matches its replica. After that verification, the loaded value can be copied to another register [16,17,18]. Thus, since loads are not replicated, they are also considered "synchronization" points. An example with the original and its corresponding replicated code is shown in Figure 1-(a) and (b), respectively. The replicated code contains additional instructions and uses additional registers marked with a '. The additional instructions are shown in bold and numbered. Instructions 1 and 2 check that the load is loading from the correct address, instruction 3 copies the value in r3 to r3', instruction 4 replicates the addition, and instruction 5-8 check that the store writes the correct data to the correct memory address.

|                   | cmp r6, r6' (1)<br>jne faultDet (2)                    |                                             |

|-------------------|--------------------------------------------------------|---------------------------------------------|

| ld r3=[r6]        | ld r3=[r6]<br>mov r3'=r3 (3)                           | ld r3=[r6]                                  |

| <br>add r4= r3,1  | add r4= r3,1<br>add r4'=r3',1 (4)                      | <br>add r4= r3,1<br><b>add r4'=r3,1</b> (4) |

|                   | cmp r4, r4' (5)<br>jne faultDet (6)<br>cmp r6, r6' (7) | <br>cmp r4, r4' (5)<br>jne faultDet (6)     |

| store [r6]=r4     | jne faultDet (8)<br>store [r6]=r4                      | store [r6]=r4                               |

| (a) Original code | (b) Replicated code                                    | (c) Safe registers                          |

Fig. 1. Example of baseline software replication and checking

#### 3 Use of Boolean Logic to Find Outcome Tolerant Branches

In this Section we explain how to use boolean logic to reduce the amount of replicated instructions. We first do an overview (Section 3.1) and then explain the compiler algorithm (Section 3.2).

#### 3.1 Overview

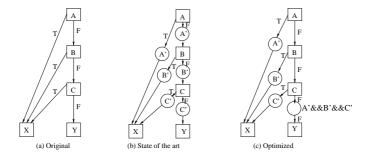

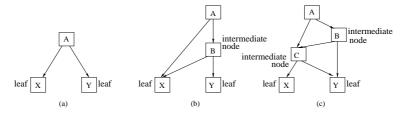

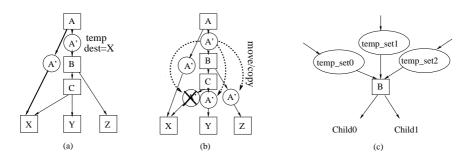

Our technique is based on the fact that programs have redundancy. For instance, Wang et al. [19] performed fault injection experiments and found that about 40% of all the dynamic conditional branches are outcome tolerant. These are branches that, despite an error, converge to the correct point of execution. These branches are outcome-tolerant due to redundancies introduced by the compiler or the programmer. An example of outcome-tolerant branch appears in a structure such as if (A | | B | | C) then X else Y. In this case if A is erroneously computed to be true, but B or C are actually true, this branch is outcome tolerant, since the code converges to the correct path. The control flow graph of this structure is shown in Figure 2-(a).

The state-of-the-art approach to check for errors is to replicate branches as shown in Figure 2-(b), where the circles correspond to the branch replicas. However, we can reduce overheads by removing the comparison replica when the branch correctly branches to X. If the original comparison in A is true we need to execute the comparison replica to verify that the code correctly branches to X. However, if A is false, we can skip the execution of the A replica and move to check B. We will only need to execute the A replica if both B and C are also false. The resulting control flow graph is shown in Figure 2-(c). In situations where A and B are false, but C is true, we can save a few comparisons.

Outcome tolerant branches also appear in code structures such as if (A & B & C) then X else Y, and in general in all the code structures that contain one or more shortcut paths in the control flow graph. A basic *shortcut path* is edge(A->X) in Figure 3-(a), where both A and its child point to the same block. However, most shortcut paths are more complex. For instance, in Figure 3-(b), block A points to the same block pointed by its grandchild (not its direct

Fig. 2. Eliminating replicated predicate evaluation

Fig. 3. Shortcut graphs and optimizations

child). Thus, the optimizer should move A' from edge(A->B) to edge(B->Z) and edge(C->Y). The example in Figure 3-(c) can be optimized in two different ways. If A and B are considered as a whole unit, edge(B->Y) is the shortcut path, and the graph can be optimized as shown in Figure 3-(d); otherwise, it can be optimized as shown in Figure 3-(e).

Detecting the existence of a shortcut path is not sufficient to determine that there is an outcome tolerant branch. The reason is that one of the blocks involved in the shortcut can modify a variable that is later used by instructions outside the block. That block needs to be replicated or the error could propagate outside the block. Next we show two examples:

- (a) if (\*m > 0) && (m < N) then X else Y

- (b) if (t=(\*m > 0)) && (m < N) then X else Y

In the example in (a), if (\*m>0) is mistakenly computed as True, but (m<N) is False, we can safely ignore the error on (\*m>0) and take the Y path. However, if the error occurs to the example in (b), and t is used in Y, ignoring the error will result in a wrong value for t being propagated to Y, which may end up corrupting the system. To avoid this type of errors our compiler algorithm only considers blocks that are involved in a shortcut path and produce values that are only used by the block itself.

#### 3.2 Compiler Algorithm

Our algorithm analyzes the control flow graph of the original program and extracts the shortcut paths and the related blocks. A *shortcut graph* always has a head node (block A in all the examples in Figure 3), one or more intermediate nodes (like B and C), two or more leaves (like X and Y), and one or more shortcut paths. Notice that in this paper we call a *block* to a single basic block or a list of basic blocks connected one by one with edges of unconditional branches.

Fig. 4. Constructing potential shortcut graphs

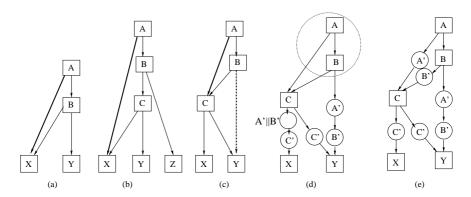

Our algorithm has two phases: first a search of all potential shortcut graphs, and second, the optimization and appropriate placement of the replicas.

Shortcut Graphs Search. The searching process starts by classifying each block as an intermediate node or a leaf, and building an intermediate node set and a leaf set. A block is called "intermediate node" if it ends with a conditional branch and does not contain side effects (does not contain a function call, a memory write or generates a value used by another block). In addition, to avoid being trapped in loops, we require that none of the outgoing edges of an intermediate node is a loop backward edge. If the node does not classify as intermediate node, then it is considered a "leaf", meaning that this block can be at the most an ending node in a shortcut graph. At the same time we build the intermediate and leaf sets, we also build a separate head node set. A block is called "head node" if it ends with a conditional branch and none of the outgoing edges is backwards, no matter it has side effects or not. Thus the head node set contains all intermediate nodes and some of the leaves.

After building the intermediate node set, the leaf set, and the head node set the shortcut graphs are built from bottom to up by scanning the head node set repeatedly. We start by initializing an empty set "graph-head-set", which will contain temporary graph head nodes. For any node(A) in the head node set, we check its two children (see Figure 4):

- 1. If the two children are leaves, this node is added to the graph-head-set (Figure 4-(a)).

- 2. If one child is a leaf(X) and the other child is an intermediate node(B) and node(B) is already in the graph-head-set, node(B) is replaced by the current node(A) in the graph-head-set (Figure 4-(b)). We also check if the leaf(X) is a child or grandchild of node(B), in which case a shortcut path for node (A) is marked.

- 3. If the two children are both intermediate  $\operatorname{nodes}((B) \operatorname{and} (C))$  and both are in the graph-head-set, nodes (B) and (C) are replaced by  $\operatorname{node}(A)$  in the graph-head-set (Figure 4-(c)). We also check if (A) introduces new shortcut paths.

Fig. 5. Optimizing shortcut graphs

The scan continues until all the nodes in the head node set have been visited. Then, a node in the graph-head-set represents a graph led by this node together with the shortcut paths found. A final pass traverses the graph-head-set and removes those heads that do not contain any shortcut path.

Optimization. After the shortcut paths are found we start applying the optimization, but we first check when it is legal to perform it. In Figure 2-(b), our optimization will move the replica A' from edge(A->B) to edge(C->Y). However, this is only legal if A dominates C. Otherwise A' may use undefined values in the new position. Thus to apply our optimization phase we first verify the domination relationship of all shortcut paths.

The goal of our optimization pass is to move replicas of the non-shortcut path down to the edge/s between the last child and the leaf/leaves. Next, we explain how this algorithm proceeds using the example in Figure 5. For each shortcut graph in the graph-head-set the algorithm finds all the shortcut paths (edge(A->X) in Figure 5-(a)), marks the replica (A') on the other path as temporary (temp), and records the destination of the shortcut path (X). Next the optimization pass scans all the intermediate nodes in the shortcut graph in a top-down fashion, and moves temporary replicas from the incoming edges to all the outgoing ones, except to those where the recorded destination of the replica and the destination of the intermediate node that we are processing are the same (an example is shown in Figure 5-(b)). Notice that when an intermediate node has multiple incoming edges (as shown in Figure 5-(c)) we only move the replicas that appear on all the incoming edges. Also notice that this optimization pass processes nodes top-down, and it does not treat multiple nodes as a single unit. Thus, for the example in Figure 3-(c), the optimized version after this pass will be the one shown in Figure 3-(e).

Finally note that A, B and C can contain computations like (s+1) == 5. In this case, if the computations are only used to determine the outcome of the branch, the computation replicas are also eliminated when the branch replica does not need to execute.

#### 4 Removal of Address Checks

Recent experiments have shown that faults produce not only data corruption, but also events that are atypical of steady state operation and that can be used as a warning that something is wrong [11]. Thus, we can reduce the overhead of the software approaches and trade reliability for performance by reducing the replication, hoping that the error will manifest with these atypical events.

In this Section we consider the removal of address checks before load and store instructions. Errors in the registers containing memory addresses may manifest as segmentation faults. However, any fault-tolerant system must also include support for roll-back to a safe state and thus, on a segmentation fault we can roll-back and re-execute, and only communicate the error to the user if it appears again. However, by doing this the system will be vulnerable to errors, since some of these faulty addresses will access a legal space and the operating system will not be able to detect the error. Thus, this technique will decrease error coverage. Next, we discuss two techniques that the compiler can use to determine which load and store instructions are most suitable for address check removal.

Address checks can be removed when there are later checks checking the same variable. For example, in Figure 1-(b), checking instructions (1-2) and (7-8) are checking the register r6. This makes the first check (1-2) unnecessary, because if an error occurs to r6 it will manifest as a segmentation fault or will be eventually detected by the checking instructions (7-8). We have observed many of these checks in the SPEC benchmarks due to the register indirect addressing mode, since the same register is used to access two fields of a structure, or because two array accesses share a common index. Removing these replicated checks can significantly reduce the software overhead.

Address checks can also be removed when the probability of error to the loaded value is small. This case appears in pointer chasing, where the data loaded from memory is used as the address for a subsequent load. An example is shown in Figure 6-(a) and (b). In this case, since the processor will issue the second load as soon as the first one completes, the probability of error is very small. In some cases, however, the value loaded by the first load is not exactly the one used by the next load, if not that it may be first modified by an add instruction. This occurs when accessing an element of a structure that is different from the first one. In this case, the probability of error is higher, and the checking instructions will also determine if an error occurred during the computation of the addition. An example is shown in Figure 6-(c) and (d).

| ld r2=[r1] | ld r2=[r1]             | ld r2=[r1]   | ld r2=[r1]                      |

|------------|------------------------|--------------|---------------------------------|

| ld r3=[r2] | cheek r2<br>ld r3=[r2] | add r4=r2,16 | add r4=r2,16<br><b>check r4</b> |

|            |                        | ld r3=[r4]   | ld r3=[r4]                      |

| (a)        | (b)                    | (c)          | (d)                             |

Fig. 6. Address check removal for pointer chasing

In this paper we evaluate the removal of the address checks for only the loads, or for both loads and stores. Thus, our results are an upper bound on the performance benefit that we can obtain and the reliability that we can lose. In the future we plan to write a data flow analysis to identify the checks that are safe to remove, as explained above.

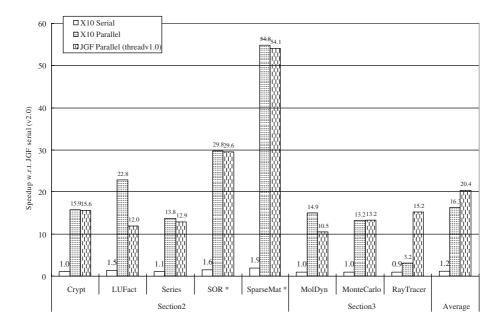

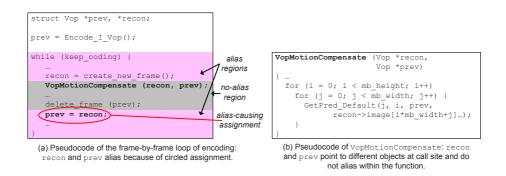

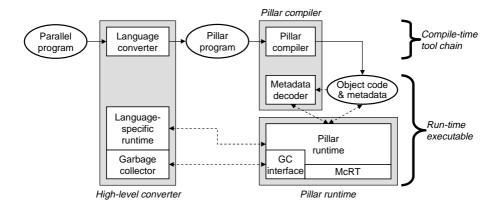

# 5 Register Safe Platforms